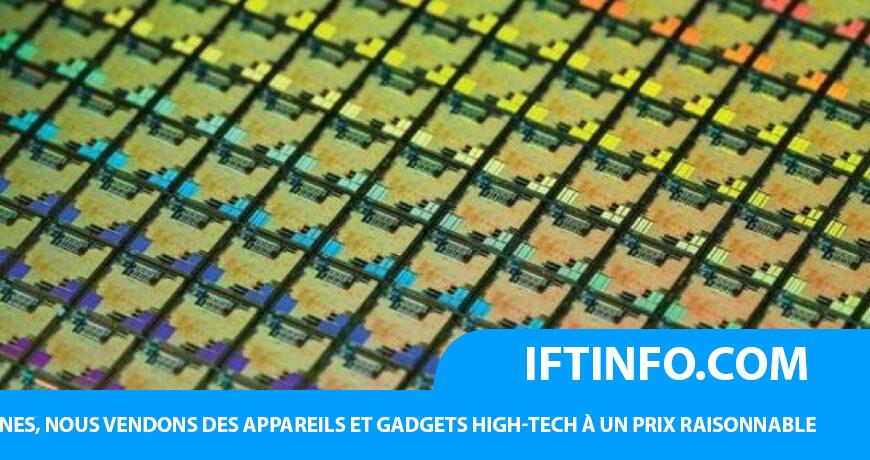

IFTINFO – Les puces 3 nm de TSMC arrivent en 2023, 2 nm en 2025 laissez un commentaire

[ad_1]

TSMC a détaillé son calendrier de développement de puces lors de son symposium technologique TSMC 2022. Le fabricant de puces basé à Taïwan introduit des puces 3 nm au cours du second semestre de cette année et apportera la technologie 2 nm sur la scène mondiale en 2025. Le nœud 3 nm se déclinera en cinq niveaux, chacun plus puissant, plus dense en transistors et plus efficace – N3, N3E (amélioré), N3P (performance améliorée), N3S (densité améliorée) et N3X (ultra haute performance). Quant au nœud 2 nm, il augmentera les performances de 10 % à 15 % à la même consommation d’énergie, et apportera une consommation inférieure de 25 % à 30 % à la même fréquence et au même nombre de transistors, par rapport au nœud N3E. N2 augmente la densité de puces par rapport à N3E de 1,1x. TSMC a introduit les GAAFET (transistors à effet de champ tout autour de la porte). Les nouveaux transistors à nanofeuilles augmenteront les performances par watt en réduisant la résistance. Pendant ce temps, Samsung Foundry commencera également à produire en masse des puces 3 nm en 2022, mais prévoit également de commencer à produire des puces 2 nm en 2025. source | Via 1 | 2

[ad_2]