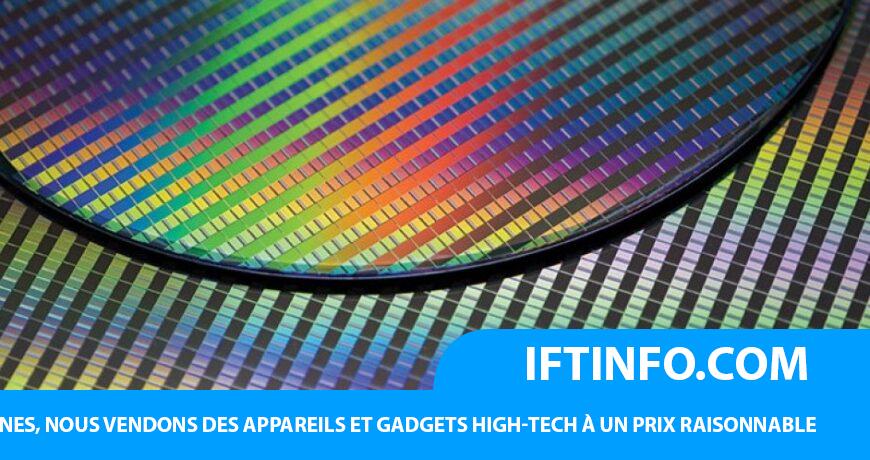

IFTINFO – TSMC présente son procédé 1,6 nm avec des gains de performances et d’efficacité significatifs laissez un commentaire

[ad_1]

TSMC a annoncé son processus de fabrication révolutionnaire de 1,6 nm pour les puces, qui comprend également un réseau d’alimentation électrique arrière qui améliore encore davantage l’efficacité énergétique et la densité des transistors. Le processus 1,6 nm annoncé repose sur des transistors nanofeuilles à grille complète, tout comme les prochaines architectures N2, N2P et N2X basées sur le nœud 2 nm. Le nouveau processus à lui seul permet des vitesses d’horloge 10 % plus élevées à la même tension et une consommation d’énergie jusqu’à 20 % inférieure à la même fréquence et à la même complexité. Selon la conception de la puce, le nouveau procédé 1,6 nm peut également accueillir jusqu’à 10 % de transistors en plus. Le réseau d’alimentation électrique arrière est sans doute un aspect encore plus impressionnant de ces futures puces, car il permet une densité de transistors accrue et une alimentation électrique améliorée, ce qui affecte à son tour les performances. TSMC affirme qu’avec le Super Power Rail (SPR), qui est le type de prise utilisé pour connecter la puce à la source d’alimentation, le réseau d’alimentation électrique arrière s’avérera principalement bénéfique pour les processeurs IA et HPC qui nécessitent un câblage de signal complexe et dense. réseaux électriques. Le calendrier de production est prévu pour le second semestre 2026, si tout se passe comme prévu, avec l’expédition des premiers produits prêts à la consommation en 2017. Source

[ad_2]